近日,中国科学院计算技术研究所的研究人员在《基础研究》杂志上发表了论文《The Big Chip: Challenge, Model and Architecture》,讨论了光刻和小芯片(Chiplet)的局限性,并提出了一种称之为“大芯片”的架构。论文介绍了一种先进的256核多芯片计算复合体,名为“Zhejiang”。

中国科学院计算技术研究所的研究人员构建并设计了一个基于16芯片的256核处理器系统——Zhejiang大芯片。

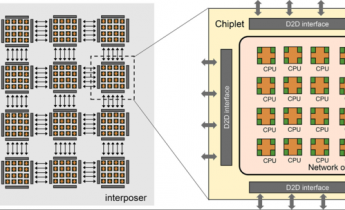

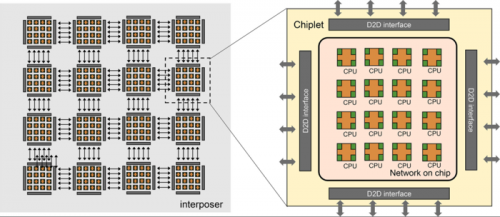

Zhejiang大芯片采用可扩展的平铺(tile-based)架构,由16个小芯片组成,它有可能扩展到100个小芯片。在每个芯片中,有16个CPU处理器通过片上网络(NOC)连接,每个芯片完全对称互连,以实现多个芯片之间的通信。CPU处理器是基于RISC-V指令集设计的。此外,该处理器采用了统一的内存系统,这意味着任何内核都可以直接访问整个处理器上的内存。

为了连接多个小芯片,采用了D2D ( Die-to-Die ) 接口。该接口采用基于时间复用机制的信道共享技术进行设计。这种方法减少了芯片间信号的数量,从而最大限度地减少了I/O凸起和中间层布线资源的面积开销,从而可以显着降低基板设计的复杂性。这些小芯片被终止于最上层的金属层,在那里构建了微I/O衬垫。Zhejiang大芯片处理器采用22纳米CMOS工艺设计制造。