·随着背面供电技术的完善和新型2D通道材料的采用,英特尔正致力于继续推进摩尔定律,在2030年前实现在单个封装内集成1万亿个晶体管。

·包括PowerVia背面供电技术、用于先进封装的玻璃基板和Foveros Direct技术预计将在2030年前投产。

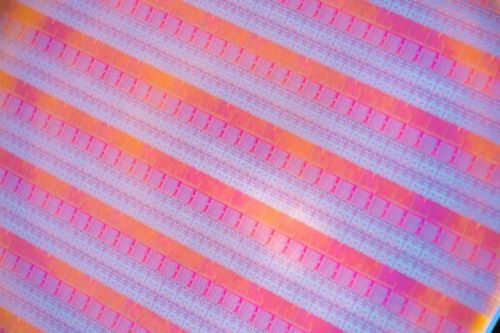

12月9日,英特尔在IEDM 2023(2023 IEEE 国际电子器件会议)上展示了使用背面电源触点将晶体管缩小到1纳米及以上范围的关键技术。英特尔表示将在2030年前实现在单个封装内集成1万亿个晶体管。

PowerVia背面供电技术预计将于2024年随Intel 20A制程节点推出。

英特尔表示,其将继续推进摩尔定律的研究进展,包括背面供电和直接背面触点(direct backside contacts)的3D堆叠CMOS晶体管,背面供电研发突破的扩展路径(如背面触点),并在同一块300毫米晶圆上(而非封装)中实现硅晶体管与氮化镓(GaN)晶体管的大规模单片3D集成。

随着遵循摩尔定律的半导体技术不断推进,半导体芯片的集成度越来越高,目前衡量芯片的微观集成密度的单位也从纳米转向埃米(1埃米等于一百亿分之一米,是纳米的十分之一)。

“我们正在进入制程技术的埃米时代,展望‘四年五个制程节点’计划实现后的未来,持续创新比以往任何时候都更加重要。”英特尔公司高级副总裁兼组件研究总经理桑杰·纳塔拉詹(Sanjay Natarajan)表示,“英特尔展示了继续推进摩尔定律的研究进展,这显示了我们有能力面向下一代移动计算需求,开发实现晶体管进一步微缩和高能效比供电的前沿技术。”

据国际数据公司(IDC)预计,全球人工智能硬件市场(服务器)规模将从2022年的195亿美元增长到2026年的347亿美元,五年复合增长率达17.3%。其中,用于运行生成式人工智能的服务器市场规模在整体人工智能服务器市场的占比将从2023年的11.9%增长至2026年的31.7%。

据英特尔透露,包括PowerVia背面供电技术、用于先进封装的玻璃基板和Foveros Direct技术预计将在2030年前投产。

英特尔技术发展总监毛罗·科布林斯基(Mauro Kobrinsky)表示:“摩尔定律推动着更多晶体管的集成,这又推动着更多的层次和更小的导线,增加了复杂性和成本。每一层次都必须提供信号和电源导线,这通常会导致优化妥协和资源争夺,形成互联瓶颈,事情变得越来越具有挑战性。”“背面电源从根本上改变了这种情况,通过在器件的两侧和垂直互连中使用电源过孔。我们明年将能够在半导体Intel 20A(2nm)和18A(1.8nm)中部署这项技术,这意味着在前面减少导线,因此我们可以放宽间距,不再需要进行优化妥协。”

“在电源过孔之外,我们的研究还涉及背面接触,这使我们首次能够连接器件两侧的晶体管。我们已经能够在研究中制造这些接触,并且前后接触无需使用电源过孔进行布线。这使我们能够减小电池的电容,提高性能并降低功耗。”科布林斯基说。

英特尔认为,晶体管微缩和背面供电是满足世界对更强大算力指数级增长需求的关键。随着背面供电技术的完善和新型2D通道材料的采用,英特尔致力于继续推进摩尔定律,在2030年前实现在单个封装内集成1万亿个晶体管。