日前,清华大学自动化系戴琼海院士团队与电子工程系联合攻关,提出了一种“挣脱”摩尔定律的全新计算架构:光电模拟芯片,算力达到目前高性能商用芯片的3000余倍。相关成果以“高速视觉任务中的纯模拟光电芯片”为题,以长文形式发表在《自然》期刊上。

1965年,英特尔创始人之一戈登·摩尔提出影响芯片行业半个多世纪的“摩尔定律”:预言每隔约两年,集成电路可容纳的晶体管数目便增加一倍。半导体领域按摩尔定律繁荣发展了数十年,“芯片”,成为人类迈入智能时代的重要引擎。然而随着晶体管尺寸接近物理极限,近十年内摩尔定律已放缓甚至面临失效。如何构建新一代计算架构,建立人工智能时代的芯片“新”秩序,成为国际社会高度关注的前沿热点。

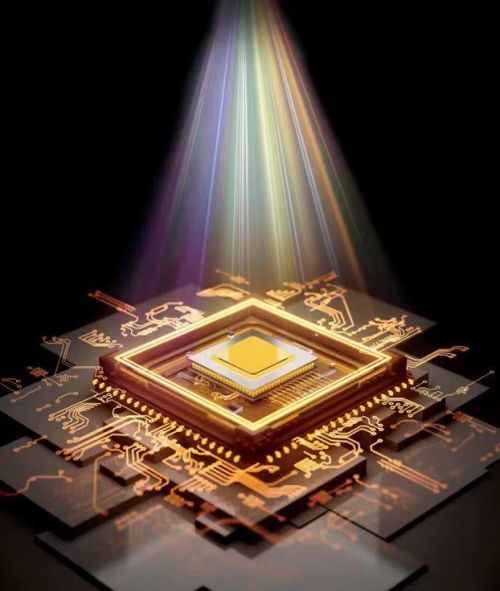

图为光电芯片

针对这一难题,清华大学自动化系戴琼海院士、吴嘉敏助理教授与电子工程系方璐副教授、乔飞副研究员联合攻关,提出了一种“挣脱”摩尔定律的全新计算架构:光电模拟芯片,算力达到目前高性能商用芯片的3000余倍。如果用交通工具的运行时间来类比芯片中信息流计算的时间,那么这枚芯片的出现,相当于将京广高铁8小时的运行时间缩短到8秒钟。

在这枚小小的芯片中,清华大学攻关团队创造性地提出了光电深度融合的计算框架。从最本质的物理原理出发,结合了基于电磁波空间传播的光计算,与基于基尔霍夫定律的纯模拟电子计算,“挣脱”传统芯片架构中数据转换速度、精度与功耗相互制约的物理瓶颈,在一枚芯片上突破大规模计算单元集成、高效非线性、高速光电接口三个国际难题。实测表现下,光电融合芯片的系统级算力较现有的高性能芯片架构提升了数千倍。然而如此惊人的算力,还只是这枚芯片诸多优势的其中之一。

在研发团队演示的智能视觉任务和交通场景计算中,光电融合芯片的系统级能效(单位能量可进行的运算数)实测达到了74.8 Peta-OPS/W,是现有高性能芯片的400万余倍。形象地说,原本供现有芯片工作一小时的电量,可供它工作500多年。

目前限制芯片集成极限的一个关键因素,就是过高密度带来的散热难题。而在超低功耗下运行的光电融合芯片将有助于大幅度改善芯片发热问题,为芯片的未来设计带来全方位突破。

更进一步,该芯片光学部分的加工最小线宽仅采用百纳米级,而电路部分仅采用180nm CMOS工艺,已取得比7纳米制程的高性能芯片多个数量级的性能提升。同时,其所使用的材料简单易得,造价仅为后者的几十分之一。

在清华大学团队提出的超高性能光电芯片下,“未来计算机”的诞生似乎已不再遥远。光电融合的新型架构,不仅开辟出这项未来技术通往日常生活的一条新路径,还对量子计算、存内计算等其他未来高效能技术与当前电子信息系统的融合深有启发。《自然》期刊特邀发表的该研究专题评述也指出:“或许这枚芯片的出现,会让新一代计算架构比预想中早得多地进入日常生活。”